Процессор «Эльбрус» — российский процессор VLIW-архитектуры с повышенными требованиями к безопасности. JVM — сложная динамичная система, которая подразумевает определенную свободу в реализации и исполнении. Эти вещи всегда вступают в противоречие друг с другом.

В докладе я расскажу про:

- особенности архитектуры и принципиальные отличия от x86,

- портирование OpenJDKZero и реализации LLVMбэкенда для Эльбруса,

- разработку VLIWкодогенератора, способного работать в условиях JITкомпилятора,

- «сращивание» кодогенератора и Optoкомпилятора,

- сборку мусора «напрямую» в регистрах процессора,

- обработку исключений и деоптимизацию при закрытых адресах возврата,

- неявные проверки границ массивов, а также про многое другое.

В результате слушатели узнают про подходы и нетривиальные решения, которые были применены при портировании JVM под «экзотическую» архитектуру, про то, каким образом использование, казалось бы, незначительных особенностей архитектуры может дать куда большее ускорение, нежели различные классические оптимизации, а также почему все говорят, что Эльбрус медленный, и насколько это является правдой.

Роман Артемьев и Сергей Андреенко, Унипро

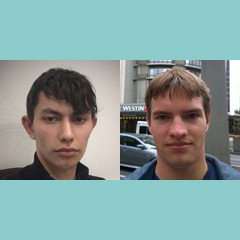

Роман Артемьев, Унипро

Более трех лет занимается одновременно Java и Эльбрусом. За это время успел покопаться практически во всех частях Hotspot VM, изучить архитектуру, поучаствовать в написании нескольких динамических компиляторов. А количество багов, которые были обнаружены и исправлены уже не поддается исчислению. Просто обожает низкий уровень, нетривиальные решения, сложные задачи, а также делиться всем этим с другими.

Сергей Андреенко, Унипро

Занимается разработкой компиляторов 4 года. Начинал карьеру в Intel в командах Intel GT compiler и Intel Compiler Perfomance Team. Проходил стажировку в Microsoft в команде Phoenix compiler infrastructure и LLILC (LLVM based MSIL Compiler). Последние 2 года работает в компании Унипро над проектом JVM для Эльбруса. Разрабатывает и поддерживает внутри- и межблоковое планирование инструкций.